Hello everyone! It's time for a day of study. Today we talk about FPGA design and development. What are the design specifications? From the documentation to the project creation, etc. You may learn a lot and take a lot of detours!

In the team project development, in order to make the development efficient, consistent, and correct, the team should have a standardized design process. Complete the project design and development work according to the specifications, classify the project folder level clearly; the project should have a good style and complete documentation, such as design ideas and debugging records and device selection; code writing efficiency, that is, a unified writing Specification, the information contained in the file header is complete, and it can be seen at a glance whether you or your team read it.

First, document naming:

The clear document naming can make our thinking very clear, so the catalog of FPGA project folder is clear and classified. A project must have a rigorous framework to store related documents and designs. It is not only convenient for self-viewing, but also improves the team's work efficiency.

Here's an example to illustrate:

The first-level folder is the project name and the second-level folder is multiple:

Used to store source files Used to store Testbench files Files used to store design-related classes Used to store IP core files, etc...

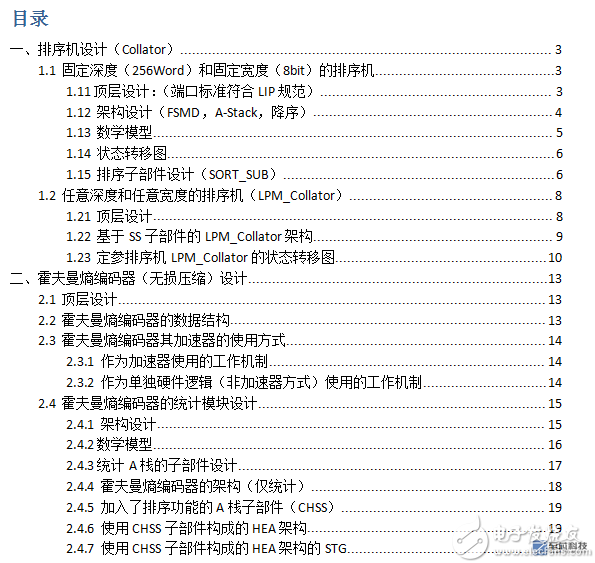

Second, design documentation:

It is beneficial to add and maintain the function of the module after recording its own ideas and debugging of the design in the document, and it is convenient for the other members of the project team to read the code when the project is jointly adjusted. It also facilitates porting between FPGAs from different vendors, as well as porting FPGAs to ASICs. The following diagram is an example of documented design. The document is clearly described and the function analysis is clear, which is beneficial to the addition and maintenance of the module function in the future.

Design idea: According to the requirements of the project, it is divided into several modules from top to bottom, and functions are written separately. The top level only acts as a description of the behavior. The logic description is written at the bottom level. The module must be programmed with hardware circuit thinking. The design of each module should consider whether there is such a hardware circuit and use synchronous design as much as possible.

Third, the programming style:

Each module should exist in a separate source file, and the source file name should be the same as the module name it contains. Each design should have a complete file header, including the company name, designer, design time, file name, belonging items, module names and functions, revision records, and version information. The identifier in the code adopts the traditional C language naming method. The words are separated by underscores, and the word naming identifiers that are meaningful and can reflect the characteristics, roles, and properties of the objects are used to enhance the readability of the program. In order to avoid the identifier being too lengthy, longer words may be abbreviated as appropriate.

Fourth, the code specification:

Active low signal, suffix name "_n", such as active low reset signal "rst_n"

Module names and signal names should be lowercase, lowercase variable names should be lowercase, such as wire, reg, input, output, and other defined variables should be named according to the function of the variable in English, succinctly expressed "xxx_xxx_xxx", to avoid too long to use uppercase letters to define constant parameters, parameter names Less than 20 letters, such as parameter TIME=20

The clock signal should be prefixed with "clk" and the reset signal should be prefixed with "rst"

The output signal of the top-level module is registered as far as possible. The three-state logic avoids the use of sub-modules. The interface signals of other modules can be used at the top-level module. Press: Input, (two-way), output order defines the port. A module must have at least one input. Output, expressions that avoid writing empty module clock events in the form of "posedge" or "negedge" Nesting If statements can't be too much advice Do not use an include statement Proposing adding timescale to each module

The necessary comments are given in the code. Each file has a header file. Each file contains only one module. Module name and file name are consistent. Asynchronous reset, use if(xxx==1'b1) or if(xxx==1'b0)

There is only one clock signal in the always block of the synchronous sequential logic, and synchronous design is used in the same edge action to avoid using asynchronous logic. Do not use the clock signal as the input of the data signal Do not add any buffer to the clock path.

In the top-level module, the clock signal must be visible. Do not define a set of clock signals in a vector-defined manner. Do not generate clock signals in the module. Use pll to generate as much as possible without using tasks. Do not use event variables. Do not use system functions. Do not use disable statements. Forever, repeat, while and other loop statements do not use non-synthesized operators There is only one list of events in an always statement. The shift variable must be a constant. A non-blocking assignment combination logical block is used uniformly in a temporal logical block. Blocking assignments

The antenna assembly harness are passed heat and other kinds of tested.

This is auto cable .OEM/ODM specification for you.welcome to your inquiring with drawing pictures or sample.

If sample offered by clients ,according machines inspection, datas of this kind of cable will be know by our technician .

If only drawing pictures ,please offer the 3D drowing pictures.

Custom Wiring Harness,Copper Material Wire Harness,Board Connector Terminal Wire Harness,Antenna Assembly Harness

Dongguan YAC Electric Co,. LTD. , https://www.yacentercn.com