MicroBlazeTM is an important component of the Xilinx embedded product line. MicroBlaze is a full-featured FPGA-optimized 32-bit computer (RISC) soft processor with fewer instruction sets to meet a variety of application needs, such as industrial, medical, automotive, consumer, and communications infrastructure markets. The MicroBlaze is a highly configurable, easy-to-use processor for use in FPGAs and the All Programmable (AP) SoC product family. It comes with Vivado® Design and System Edition and Vivado Webpack Edition for free. In addition, it is available as part of the original IDS embedded version for older FPGA device families such as Spartan®-6 and Virtex®-6.

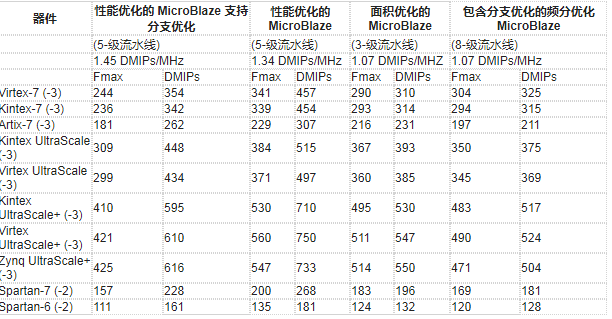

MicroBlaze is a highly configurable IP core that supports more than 70 configuration options. Some important configuration options are instruction/data cache, floating point unit, and memory management unit. Users can use a highly flexible, configurable core to achieve virtually any processor use case, from very small state machines or microcontrollers to high-performance computing-intensive microprocessor systems running Linux. The IP can be configured to operate in three-stage pipeline mode (optimized for size) or configured to operate in five-stage pipeline mode (optimized for speed), thus providing more than any other FPGA soft processing solution Fast DMIP performance.

MicroBlaze performance metrics: based on Vivado 2017.3

Note: Because of the Zynq-7000 device, the Zynq-7000 AP SoC has the same performance values ​​as Artix-7 and Kintex-7.

Simplify your life - the MicroBlaze Configuration Wizard!

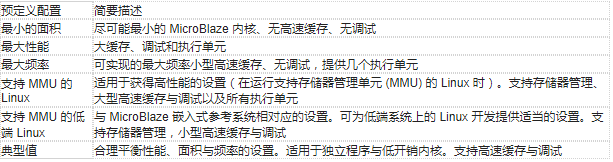

For highly configurable MicroBlaze processors, Xilinx provides configuration wizard tools for ease of use. This tool provides users with predefined quick configuration options. Users do not need to configure from more than 70 options, and can choose predefined options based on use cases. The following table shows the various predefined options and typical use case descriptions.

Key features of MicroBlaze (including configurable features/options): Users can choose a two-step configuration process: the first step selects the predefined configurations listed in Table 1; the second step adjusts several selected configuration options to fit them Actual use case.

Level 3 or 5 pipeline support

Support for native AXI-4

Support for AXI Consistency Extension (ACE)

Cache line word length: 4, 8, or 16

Area and speed optimized configuration options

Support memory management unit

Support low latency interrupt mode

Fault tolerance, including error correction code (ECC) and lockstep support

MPU mode for regional protection of secure RTOS applications

Instruction and data cache

Cache size configurable: 2kB - 64kB (based on module RAM)

Local Memory Bus (LMB) instruction and data interface.

Hardware barrel shifter

Hardware multiplier and divider

Up to 16 AXI data stream interfaces

Floating point unit (single precision, compatible with IEEE 754)

Processor version register

Floating base vector

Support sleep mode and sleep command

Extended debugging support: performance monitoring, performance tracking, non-intrusive analysis

Crystal Clear Back Sticker,Phone Sticker,Mobile Phone Back Skin,Crystal Clear Phone Skin

Shenzhen Jianjiantong Technology Co., Ltd. , https://www.hydrogelprotectivefilm.com