1 Introduction to IEEE 1149.7 standard

The IEEE 1149.7 standard is based on the IEEE 1149.1-2001 Boundary Scan standard and is compatible with new features to support extended testing and debugging. The standard specifies a new feature of the IEEE 1149.7 test access port (referred to herein as the TAP.7 interface) structure and control timing logic, which differs from the IEEE 1149.1 standard specification test access port (TAP.1 interface) in that it can be embedded in the chip. Multiple test access port controllers (TAPCs) and classify them. The standard TAPC levels in the standard include: ADTAPC, CLTAPC, and EMTAPC, which are serially connected in the interface, and the high-level TAPC controls and manages the low-level TAPC. In terms of functional characteristics: TAP.7 interface defines 6 functional levels of T0~T5, each layer reflects the upgrade feature upwards, and the compatibility features are reflected downward. The T0 layer provides the operational behavior specified by the TAP.1 interface at startup; the T1 layer mainly adds power supply control functions; the T2 layer adds chip-level bypass function while providing a "thermal connection protection" function; the T3 layer is increased. A mechanism to support 4-wire star topology scanning; the T4 layer provides features that support 2-pin connectivity; the T5 layer adds data transfer capabilities and supports features other than boundary scan.

2 JTAG-based TAP.7 interface upgrade features

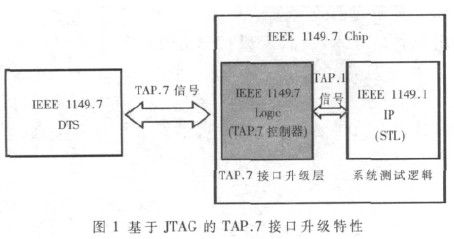

The IEEE 1149.7 test standard defines a connection between the debug and test system (DTS) based on the IEEE 1149.1 test standard and the target system (TS). This connection is represented by the addition of a standard control logic of the IEEE 1149.7 standard specification to the IEEE 1149.1 standard specification test access port [2] (referred to herein as the TAP.1 interface) to implement new functional features (referred to as adding in this document). The layer is the TAP.7 controller). The TAP.7 controller mainly provides the test debug signal of the IEEE 1149.7 standard specification and the TAP.1 interface of the IEEE 1149.1 standard specification IP to provide a compatible test debug interface (referred to as TAP.7 interface in this paper), which can be used in the original TAP.1 interface. The test connection block diagram of the upgrade function of the TAP.7 interface is shown in Figure 1.

As shown in Figure 1, the TAP controller in the TAP.7 interface upgrade layer is ADTAPC (referred to as TAPC in this paper), which mainly completes the control operation of the TAP.7 signal, thereby implementing new upgrade features and TAP. The 7-signal test and debug logic is decoded to match the timing signal of the TAP.1 interface, thereby completing the control of the IEEE 1149.1 device TAPC. IEEE 1149.1 IP can also be considered as a device with a test JTAG port conforming to the IEEE 1149.1 test standard [3] (hereafter referred to as STL hereinafter), which includes a TAP controller (collectively referred to herein as a chip-level TAPC or CLTAPC). It is a TAP interface that fully complies with the IEEE 1149.1 test standard specification. It mainly completes the control of the device's test and debug logic, thus completing the corresponding test and debug tasks.

Principle and design of 3 star scanning technology interface

The complete TAP.7 interface upgrade layer includes RSU, APU, and EPU. The RSU (Reset Select Unit) provides a reset operation and the TAP.7 controller select cancel operation. The EPU (Extended Protocol Unit) provides an IEEE 1149.1 interface primarily for the T1-T3 layer TAP.7 interface. The APU provides a narrow (2-pin) or wide (4-pin) TAP.7 interface for the T4-T5 layer, providing hardware support for advanced protocol operation. Depending on the design requirements of the actual function, the TAP.7 controller can be composed of any combination of RSU, EPU and APU, providing a bridge between the TAP.7 signal and the TAP.1 interface of the STL, and the RSU, APU and EPU The layer does not affect the length of the STL scan path.

3.1 Star scan function interface hardware design

The 4-wire star scanning topology function is defined by the T0~T3 layer of the TAP.7 interface. The technical branches that make up the star topology are generalized and can include: TAP.7 interface string topology technology branch, 4-wire star The technology branch of the topology, the string technology branch of the TAP.1 interface, and other technology branches. This paper mainly studies the scanning function of the first two technology branches sharing DTS connection. According to TAP.7 function scalability and hardware hierarchy, the hardware layer of the TAP.7 interface of the star scanning function mainly includes: RUS and EPU units. The block diagram of its hardware design is shown in Figure 2.

SHAOXING COLORBEE PLASTIC CO.,LTD , https://www.colorbeephoto.com